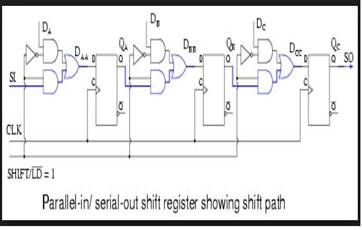

A 4-bit serial-to-parallel shift register is one of the simplest types of circuits utilising four D-type flip-flops. module SIPO ( input SERIN, input RST, input CLK, input LOAD, output reg READY, output reg 7:0 PAROUT ) parameter IDLE 2b00, START 2b01, TRANSMIT. A serial to parallel converter is a digital circuit where we feed the input data serially, and read the outputs in parallel fashion. The part: if (STATE TRANSMIT) PAROUT COUNTER SERIN seems wrong to me, but I cant understand what to change or test. Check the modified blocks with a test-bench. I guess the problem is around the second always block. If the receiver de-asserts this line, the transmitter will keep (freeze) the last bit sent on the line, until the ‘receiver ready’ signal is asserted again. Additional design details will be covered in class. The component should have 4 inputs (D3:0), a clock (CLK), a load/shift input signal (-LD/+SHF) and one serial output (Y). Same as 1, but now the ‘receiver ready’ line serves as a flow control line. Design a 4-bit parallel to serial shifter using (4) D Flip-Flops and (4) 2:1 Muxes in Quartus.Modify both blocks and test them with a modified test-bench. The Parallel to serial converter will sample this line and will start a new transmission only if this line is asserted. Also, works as Serial-to-parallel converter, if Q. Winner of the Standing Ovation Award for Best PowerPoint Templates from Presentations Magazine. Add a ‘receiver ready’ line, as an output from the Serial to parallel converter. Different approach to FSM design 9/18/07 EECS150 Fa07 Lec7 Counters 4 RS RS RS. Worlds Best PowerPoint Templates - CrystalGraphics offers more PowerPoint templates than anyone else in the world, with over 4 million to choose from.On the waveform below it can be seen the transmitted data and the received data by the ser2par module.Īll the source files for this simulation can be found here. ISRO (VSSC) Technical Assistant Electronics 2018 Official Paper. 8-Bit Serial or Parallel-Input / Serial-Output Shift Register. After four clock pulses are applied, the content of the shift register will be. The received data is available in parallel format on the data_outbus.įor the simulation, the Parallel to serial converter is used to generate data and the ser2par receives the data. The initial content of the 4 bit Serial IN Parallel Out shift register is shown in Figure is 1100. If a frame_insignal is detected, the data is latched in and the data_rdyoutput is asserted until the rdinput is asserted by the host. This VHDL module receives serial data from the data_inline.

0 kommentar(er)

0 kommentar(er)